Table Of Content

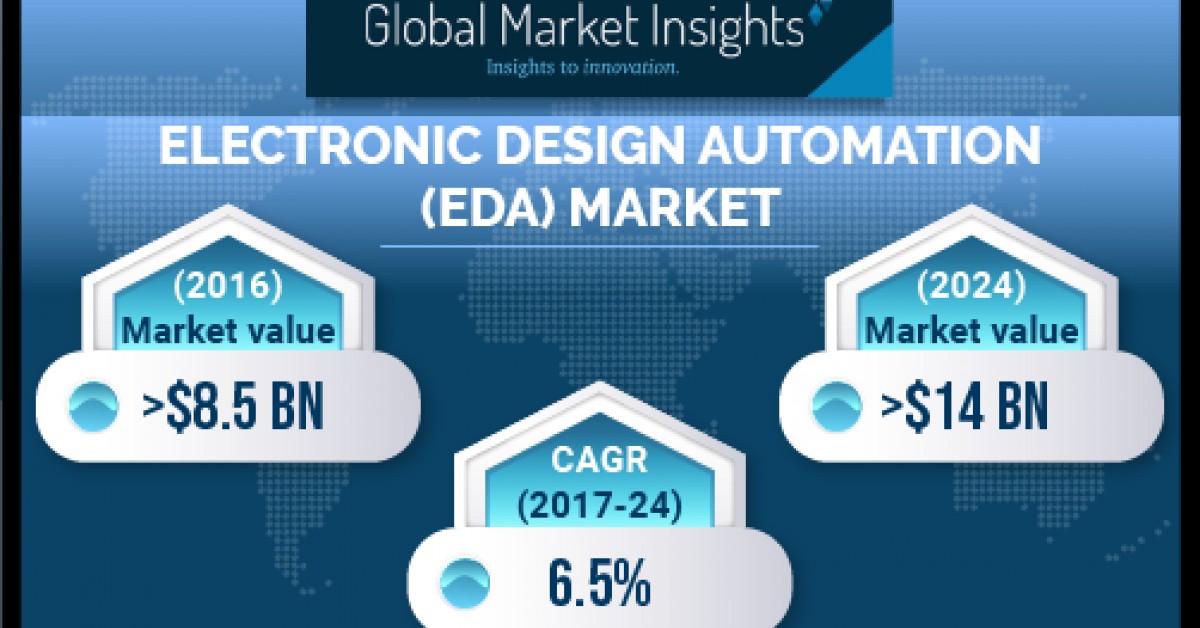

It is crucial to know they'll function as intended, especially since most chip code cannot be "patched." Instead, teams must respond to errors by revising completely. A recent Business Wire report anticipated that as the semiconductor industry grows more competitive and as new chip technology emerges, the market for EDA tools will skyrocket. The Solido variation-aware design, IP validation and library characterization solutions, powered by proprietary AI and machine learning technologies, are used by 1000s of designers at the top semiconductor companies worldwide. Calibre Design Solutions is the industry leader for IC sign-off, delivering a complete IC verification and DFM optimization EDA platform that speeds designs from creation to manufacturing, addressing all sign-off requirements.

SMITEC: Forerunners of Industrial Automation with IoT Solutions

Yet, it does demonstrate the degree to which electronic design automation can be leveraged to help improve the reliability of your PCBA design process. Other benefits of employing electronic design automation include the following. With the dramatic expansion of semiconductor technology, there is a movement toward a need for a larger platform of tools and technologies which may signal the next phase of the industry’s development. Synopsys is a leading provider of electronic design automation solutions and services. The official podcast of the Design Automation Conference, the premier conference on leading-edge research and practice in tools and methodologies for the design and design automation of electronic circuits and systems. Key topics discussed are tailored to practitioners in design and design automation ecosystem.

Call for Nominations for Editor-in-Chief of the IEEE Embedded Systems Letters

And automate the release process to streamline IP integration and improve collaboration. Calibre – Calibre is a complete IC verification and DFM optimization EDA platform that speeds designs from creation to manufacturing, addressing all sign-off requirements. It is also worth noting that the cost of an error in a manufactured chip can be catastrophic. Chips errors cannot be “patched.” The entire chip must be re-designed and re-manufactured. The time and cost of this process is often too long and too expensive, resulting in a failure of the entire project. So, the complexity to design chips is high and the need to do it flawlessly is also required.

Fabless/foundry ecosystem solutions

See how Siemens EDA supports fabless/foundry ecosystems with collaboration and innovation. For over 175 years, Siemens has helped customers innovate products and industries. With Siemens EDA and the Siemens Xcelerator portfolio, we enable customers to embrace digital transformation to accelerate the pace of innovation. But poor digital infrastructure and regulatory bottlenecks could slow adoption.

NVIDA AI accelerated library verification

Chinese Chip Design Software Devs Receive Massive Government Support - Tom's Hardware

Chinese Chip Design Software Devs Receive Massive Government Support.

Posted: Mon, 06 Nov 2023 08:00:00 GMT [source]

Leading semiconductor companies like Samsung, NVIDIA, and Texas Instruments rely on Perforce’s award-winning solutions to maximize scale. As their name suggests, verification EDA tools verify whether a chip meets expectations and performs desired behavior. Each semiconductor fab has its own requirements, with most requiring teams to meet more than a thousand rules and specifications. Verification electronic design automation technology ensures compliance, as well as compares actual function to predicted function.

Functional safety

It can also take the form of an interactive process that is guided by a designer. The first trade show for EDA was held at the Design Automation Conference in 1984 and in 1986, Verilog, another popular high-level design language, was first introduced as a hardware description language by Gateway Design Automation. Simulators quickly followed these introductions, permitting direct simulation of chip designs and executable specifications. Recent innovations in AI promise to accelerate the chip design lifecycle significantly. EDA tools are adopting more pervasive AI to increase the EDA engineer’s productivity and quality of output. Such advancements are a compelling ingredient in our own internal AMD recipes to create more innovative silicon.

Engineer a smarter future faster with Siemens EDA

These companies face challenges in setting up and maintaining hybrid or on-premise solutions. By contrast, cloud-based EDA reduces the effort customers require to achieve their performance and cost goals for the design and verification of semiconductors. AWS Software Partners and AWS Systems Integrator (SI) Partners offer solutions for EDA in the cloud, as well as guidance based on Scale-Out Computing on AWS. EDA 4.0 is transforming electronic design automation through the power of artificial intelligence and delivers several key technologies that will help engineers realize the revolutionary changes of Industry 4.0. In this article we provide a comprehensive survey of the potential contributions of machine learning in addressing various aspects of functional verification. The article highlights the typical applications of ML in functional verification and summarizes the state-of-the-art achievements in this field.

PCB Electronic Design Automation Tools

This capability is instrumental in static code analysis, requirement engineering, and coding assistance for several popular programming languages. Given enough training data, it is reasonable to believe that these techniques can train ML models for various functional verification tasks. The chips were easier to lay out and more likely to function correctly, since their designs could be simulated more thoroughly prior to construction. Although the languages and tools have evolved, this general approach of specifying the desired behavior in a textual programming language and letting the tools derive the detailed physical design remains the basis of digital IC design today. Smaller, more powerful devices across healthcare, consumer electronics, aerospace, defense, and automotive sectors require highly complex integrated circuits. EDA tools are essential in this process, allowing engineers to design, simulate, and optimize these chips efficiently.

Microsoft IP QA with Solido IP Validation

If a very large amount of input data must be processed, hardware approaches such as emulation or rapid prototyping are used. These situations occur when a processor’s operating system must be run against real-world scenarios, such as video processing. Without a hardware-assisted approach, the runtime for these cases can be untenable. Alan is a highly accomplished executive with over 20 years of experience in the technology industry.

Its unique technologies can reduce design cycles by 50 percent or more while significantly improving overall quality and resource efficiency. PADS Professional – PADS Professional is a complete PCB design platform that includes board design and analysis technologies, cloud-enabled collaboration, part research and creation, and real-time supply-chain insights. See how you can connect and your design tools into your overall processes and flows. Watch this session and learn how to leverage AWS cloud capacity for full cloud migration or peak demand expansion for custom IC verification workloads, and achieve faster time-to-market.

Further experiments on FSM and non-FSM designs have demonstrated 69% and 72% reductions compared to directed sequence generation. However, most of these results still suffer from the limitation of the statistical nature of ML. A more comprehensive review of ML-based coverage-directed test generation (CDG) gives an overview of several ML models and their experiment results.

Questa's best-in-class technologies maximize the effectiveness of verification at the IC block, subsystem, and system levels. After the chip is manufactured, there is a growing requirement to monitor the performance of the device from post-manufacturing test to deployment in the field. The goal of this monitoring is to ensure the device continues to perform as expected throughout its lifetime and to ensure the device is not tampered with. For many years, the larger electronic companies, such as Hewlett-Packard, Tektronix and Intel, had pursued EDA internally, with managers and developers beginning to spin out of these companies to concentrate on EDA as a business. Daisy Systems, Mentor Graphics and Valid Logic Systems were all founded around this time and collectively referred to as DMV. Department of Defense additionally began funding of VHDL as a hardware description language.

The Asia Pacific (APAC) region holds the leading position in the EDA market, primarily due to the concentration of semiconductor industries in countries like China, Japan, South Korea, and Taiwan. Rising demand for electronics and significant investments in semiconductor chip design contribute to the dominance of this region. Bug analysis aims to identify potential bugs, localize the code blocks containing them, and give fix suggestions. Recent surveys found that verification of an IC spends roughly the same amount of time as it does in design and that functional bugs contribute to about 50% of respins for an ASIC design. Therefore, it is critically important that these bugs can be identified and fixed in the early functional verification stage. ML has been employed to help developers detect bugs in designs and find bugs faster.

Simple code completion is a standard feature in the modern Integrated Development Environment (IDE). However, more advanced techniques involving deep learning were proposed and are maturing quickly. It is now possible to train ANNs with billions of parameters from many large-scale open-source code repositories to give reasonable recommendations of code snippets from developers’ implementation intent or the context. Classic code smell detection relies on defined heuristic rules to identify patterns in the source code. Instead of manually developing these rules and metrics in the static code analysis tools, an ML-based approach can be trained on a large amount of available source code to identify code smells.

The Universal Approximation Theorem proves that a multi-layer perceptron (MLP), a feed-forward ANN with at least one hidden layer, can approximate any continuous function with arbitrary accuracy. Whereas normalized recurrent neural networks (RNNs), a specialized form of ANN, are proven to approximate any dynamic system with memory. Advanced ML accelerator hardware has made it possible that ANNs can model the behaviors of some IC design modules to accelerate their simulations. Significant acceleration may be achieved depending on the capability of AI accelerators and the complexity of the ML models.

There is simply no way to manage this level of complexity without sophisticated automation, and EDA provides this critical technology. Without it, it would be impossible to design and manufacture today’s semiconductor devices. Synopsys is a leading provider of high-quality, silicon-proven semiconductor IP solutions for SoC designs.

No comments:

Post a Comment